¡Una Cuarta!

En la anterior tapa sobre el transistor MOSFET y la tecnología CMOS comentamos que esta adolecía de un problema, en la presente tecno-tapa intentaremos explicar este problema y su solución.

El problema más común en la tecnología CMOS se produce por la aparición de unos transistores BJT «parásitos» que pueden producir la conducción indeseada de corriente por la oblea de silicio llegando a producir incluso su destrucción, este fallo se conoce en inglés como Latch-Up y en castellano como enclavamiento.

¿Qué es el Latch-Up?

El Latch-Up es un mecanismo de fallo de los circuitos CMOS que se caracteriza por la conducción de una excesiva corriente entre el drenador y el surtidor debido a un fallo en el funcionamiento. Este fallo puede ser una condición temporal, se produce debido a un estímulo y se puede recuperar anulando tal estímulo, o puede ser una condición continua que requiera el apagado total del circuito para cortar esta conducción no deseada.

El Latch-Up es un fenómeno no-deseado pero controlable, y en muchos casos se puede evitar.

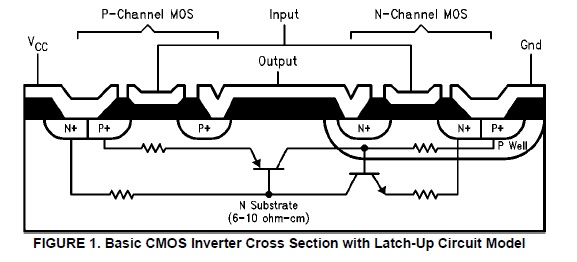

La causa de que esto exista es debido a la existencia de unos transistores BJT parásitos que se producen entre las áreas que forman los transistores MOSFET y el sustrato. En la siguiente figura se representa el corte transversal de un inversor CMOS tal y como se explicó en la anterior tecno-tapa, pero incluyendo los transistores BJT parásitos que aparecen en la oblea.

Normalmente la corriente parásita que puede circular por estos BJTs parásitos es muy pequeña, y está limitada por la resistencia que existe por la propia conductividad limitada del semiconductor.

Sin embargo esta corriente puede ser muy elevada en presencia de un stress térmico elevado, sobre-voltajes, o incluso si el integrado está sometido a un ambiente con una elevada radiación ionizante, como es el caso de procesadores que deban funcionar en el espacio.

¿Qué se puede hacer?

Cómo podemos deducir el «latch-up» es muy dependiente de las características de los transistores bipolares parásitos, es decir de la ganancia en corriente de estos, la eficiencia de los emisores, la vida media de los portadores de carga, etc. y todos estos factores están definidos, o dependen de la geometría y el proceso de fabricación.

La posibilidad del «latch-up» crece conforme aumentamos el grado de integración, es decir, el número de transistores por área que se pueden encontrar en la oblea. De esta forma vemos que habrá que buscar una solución de compromiso a la hora aumentar el número de transistores y su fiabilidad (en lo que a «latch-up» se refiere).

De esta manera, dado que el problema es geométrico, la solución al problema del enclavamiento será también geométrica. Tendremos que hacer variaciones en el proceso de fabricación de los transistores para disminuir este acoplamiento debido a los transistores parásitos, aumentando por ejemplo la conductividad en uno de los BJTs se producirá un aumento en la cantidad de corriente necesaria para que se produzca el «latch-up», como se observa en la siguiente figura:

En la figura anterior se ha añadido una capa fuertemente dopada por debajo de la capa superficial donde se construyen los transistores, de forma que esta capa hace que con el circuito debidamente polarizado, la cantidad de corriente que se tiene que inducir en el BJT NPN para que se produzca la realimentación sea mucho mayor.

Además de estas consideraciones digamos de «bajo nivel» tendremos que tener otras a la hora de construir nuestros circuitos como el aislamiento de cargas capacitivas o inductivas, precauciones con la alimentación, etc.

Pero espero que está entrada haya servido al menos para presentar uno de los problemas de la tecnología CMOS, y como se puede afrontar su solución, así como los motivos por los que se pueden producir fallos, hacer hincapié en que los circuitos integrados de uso espacial deberán tener especial cuidado, lo que ya nos da una pista de porqué no se utilizan procesadores de ultimísima generación, con una densidad muy grande de transistores por unidad de área.

Nos seguimos leyendo.

Ref.: